TSMC no es el mayor fabricante de semiconductores en el planeta por casualidad. Morris Chang fundó esta veterana compañía taiwanesa en 1987, pero su liderazgo tardó varios años en consolidarse. En ese momento, el fabricante de circuitos integrado más importante era Intel, pero El dominio TSMC En esta industria durante las últimas dos décadas es irrefensable. Hoy monopoliza aproximadamente el 60% de la fabricación de circuitos integrados, y nada indica que a corto plazo Intel o Samsung, sus dos competidores principales, podrán disputar su liderazgo.

El éxito de esta compañía se ha basado principalmente en su capacidad para fabricar chips a gran escala utilizando las tecnologías de integración más avanzadas disponibles y con un rendimiento de oblea muy alto. Aquí se encuentra su muy alta competitividad. Y, además, ha logrado preservar esta posición durante muchos años, lo que lo ha ayudado a transmitir confianza a sus clientes sólidos, como una roca. Su desempeño económico no es más que una consecuencia de su carrera: en 2024 ingresó un 34% más que en 2023.

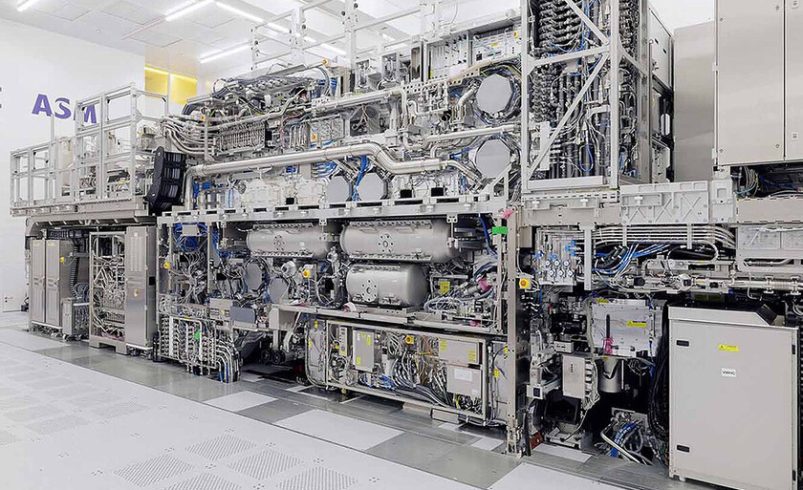

TSMC afirma poder llevar el equipo de litografía ASML UVE al límite

Este fabricante de circuitos integrado ha confirmado que las pruebas de su nodo de 2 nm están siendo exitosos, por lo que puede comenzar la fabricación a gran escala de semiconductores utilizando esta fotolitografía durante el segundo semestre de 2025. Sin embargo, sus planes a mediano plazo no terminan aquí. Y es que a fines de abril pasado anticipó durante su Conferencia Tecnológica de América del Norte que también está probando su siguiente tecnología de integración de Avant -Garde. Lo llamará A14 (1,4 nm), ingresará a gran producción a gran escala en 2028 y ya conocemos algunas de sus características más interesantes.

Kevin Zhang asegura que TSMC no necesite el equipo de litografía ASML UVE UVE High-NNA para hacer 1,4 nm

Uno de sus puntos más importantes consistirá en que usará transistores Nanoesheet GAA (Vuelta a la puerta) Segunda generación. La primera generación llegará al lado de la litografía N2 (2 nm) este año. Además, esta tecnología de integración aterrizará con la promesa de hacer posible la fabricación de circuitos integrados con mayor rendimiento, mayor eficiencia energética y un diseño más flexible. Lo habitual. Sin embargo, TSMC, afortunadamente, ha estado húmedo y, en su caso, algunas cifras se han hecho públicas que nos permiten evaluar en qué medida será importante la llegada del nodo A14.

Y, según esta compañía, los circuitos integrados producidos con la litografía A14 serán un 15% más rápidos que los chips fabricados en el Nen N2 con el mismo consumo; Reducirán el gasto de energía en un 30% a la misma velocidad y, además, pondrán sobre la mesa la posibilidad de aumentar la densidad de la lógica en un 20%. Según Kevin ZhangEl vicepresidente senior y el subdirector de operaciones de TSMC, el nodo A14 será atractivo tanto para hacer chips para dispositivos de consumo como para aplicaciones estrictamente profesionales, como, por ejemplo, GPU para inteligencia artificial (IA).

No hay duda de que las promesas de TSMC sobre su litografía A14 suenan bien, pero hay más que no debemos pasar por alto. Zhang dice que no utilizarán el equipo de fotolitografía ultravioleta extremo (UVE) y la apertura de haute (High-Na) que fabrica la empresa holandesa ASML en este nodo. Esta es una exposición de capacidad técnica. Estas máquinas, las más avanzadas que existen actualmente, son adecuadas para producir circuitos integrados de 2 nm y más allá.

De hecho, la litografía 14A (1,4 nm) será la primera en la que Intel usará el equipo UVE de alta apertura de ASML. Sin embargo, como acabamos de ver, TSMC dice que puede producir chips capaces de lidiar con semiconductores comparables de Intel y Samsung utilizando equipos UVE convencionales. 2025 será el año en que comenzarán las litografías de 2 nm y, por lo tanto, será el preludio de una batalla presumiblemente aún más sangrienta: la de los 1.4 nm.

Imagen | Asml

Más información | Hardware de Tom

En | El nuevo equipo de litografía de ASML divide a los fabricantes de chips. TSMC considera no usarlo hasta 2030